# ECN33202SP/SPR/SPV

#### **Product Description**

#### 1.1 Description

- (1) A motor is driven by three input signals (U, V, W) to ECN33202.

- (2) Dead time and six control signals from three input signals are generated in ECN33202.

- (3) Applicable to three shunt motor control method because emitter pins are set for U, V, W of bottom arm IGBTs (Insulated Gate Bipolar Transistors).

- (4) Acceptable for incoming power of AC 200V to 230V. Maximum rating: 500VDC/2.0A.

- (5) Latch-up free monolithic IC built with high voltage Dielectric Isolation (DI) technology.

#### 1.2 Functions and Features

- (1) Three input type.

- (2) Built-in dead time generation. (Top and bottom arm short-circuit protection)

- (3) Three shunt method applicable.

- (4) IGBT all off signal input pin.

- (5) Fault output pin.

- (6) Built-in charge pump circuit.

- (7) Built-in 5V power supply circuit.

- (8) Built-in over-current protection.

- (9) Built-in 15V VCC under-voltage detection.

<3-input series> P. 2/16

## ECN33202SP/SPR/SPV

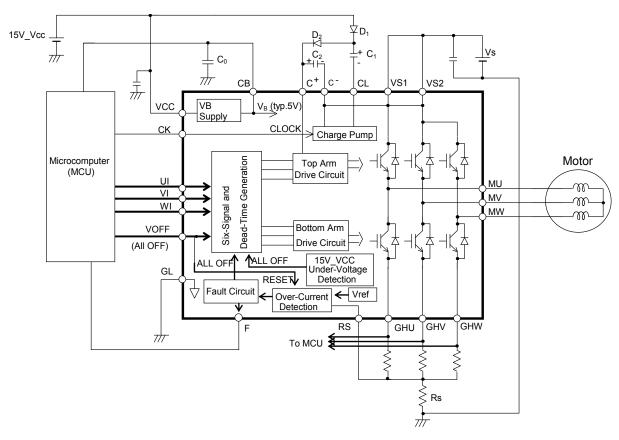

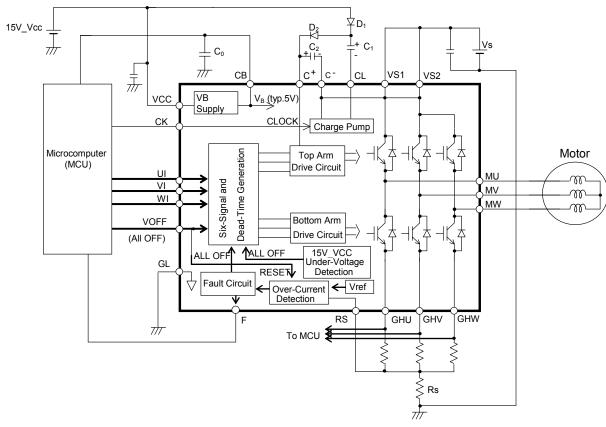

#### 1.3 Block Diagram

ECN33202 is shown inside the bold line in Fig. 1.1.

Fig.1.1 Block Diagram

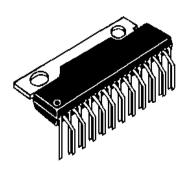

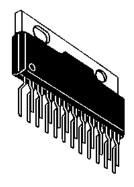

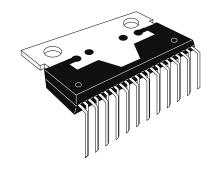

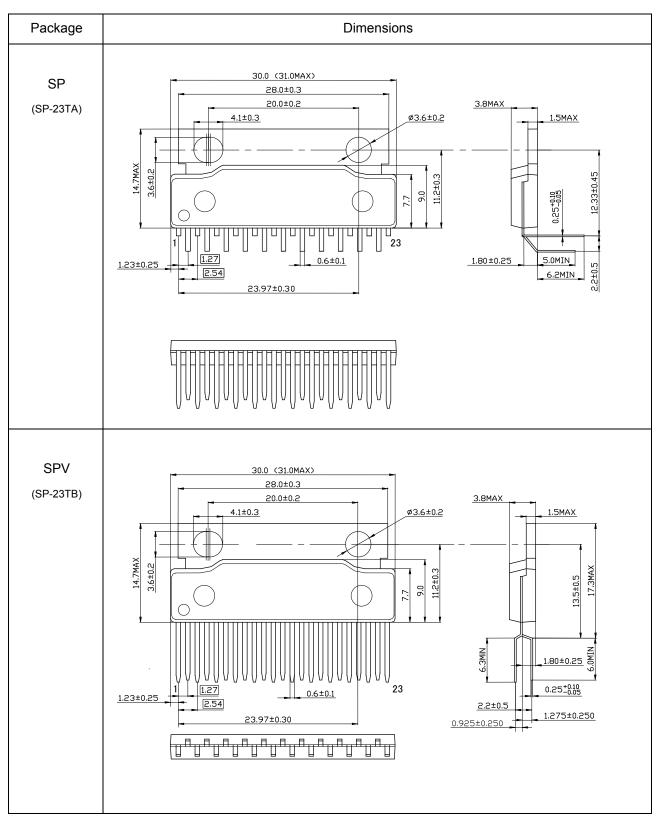

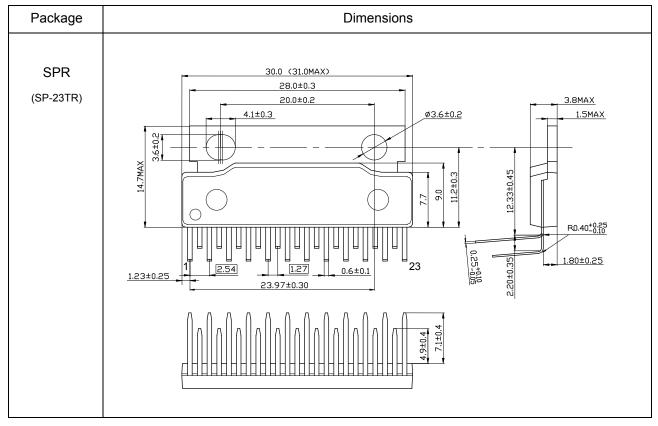

#### 1.4 Types and Packages

ECN33202SP (Package Type:SP-23TA)

ECN33202SPV (Package Type:SP-23TB)

ECN33202SPR (Package Type:SP-23TR)

Fig. 1.2 Types and Packages of ECN33202

## ECN33202SP/SPR/SPV

#### 2. Specifications

#### 2.1 Absolute Maximum Ratings

| Table | 2.1 Absolute Ma           | ximum Rating | Condition: Ta=25 °C |              |               |      |           |

|-------|---------------------------|--------------|---------------------|--------------|---------------|------|-----------|

| No.   | Item                      |              | Symbol              | Pin          | Rating        | Unit | Condition |

| 1     | Output device             |              | VSM                 | VS1, VS2     | 500           | V    |           |

|       | breakdown voltag          | е            |                     | MU, MV, MW   |               |      |           |

| 2     | VCC power supply voltage  |              | 15V_VCC             | VCC          | 18            | V    |           |

| 3     | Voltage between C+ and C- |              | VCPM                | C+, C-       | 18            | ٧    |           |

| 4     | Input voltage             |              | VIN                 | UI, VI, WI   | -0.5 to VB+0. | V    |           |

|       |                           |              |                     | CK, RS, VOFF | 5             |      |           |

| 5     | Output current            | Pulse        | IP                  | MU, MV, MW   | 2.0           | Α    | Note 1    |

| 6     |                           | DC           | IDC                 |              | 1.4           |      |           |

| 7     | VB supply output current  |              | IBMAX               | СВ           | 50            | mΑ   |           |

| 8     | Junction operating        |              | Tjop                | _            | -20 to +135   | °C   | Note 2    |

|       | temperature               |              |                     |              |               |      |           |

| 9     | Storage temperature       |              | Tstg                | _            | -40 to +150   | °C   |           |

Note 1: Output IGBTs can handle this peak current at 25 °C junction operating temperature.

Note 2: Thermal resistance

(1) Between junction and ECN33202 case (tab): Rjc=4  $^{\circ}$ C /W

(2) Between junction and air: Rja=40 °C /W

<3-input series> P. 4/16

## ECN33202SP/SPR/SPV

#### 2.2 Electrical Characteristics

Table 2.2 Electrical CharacteristicsSuffix (T: Top arm, B: Bottom arm)Condition: Ta=25°C

|     |                      |                        | i e     | ·                       | 1. 10p a |      |      |      |                                 |                    |

|-----|----------------------|------------------------|---------|-------------------------|----------|------|------|------|---------------------------------|--------------------|

| No. |                      | Item                   | Symbol  | Pin                     | Min.     | Тур. | Max. | Unit |                                 |                    |

| 1   | Standby c            | urrent                 | ISH     | VS1, VS2                | _        | 0.15 | 1.00 | mA   | VOFF=0V, C                      |                    |

| 2   |                      |                        | ICC     | VCC                     | 1        | 3    | 10   | mA   | VS=325V, VC<br>IB=0A            | CC=15V,            |

| 3   | IGBT colle           | ctor-emitter           | VONT    | MU, MV, MW              | 1        | 2.0  | 3.0  | V    | I=0.7A, VCC=15V                 |                    |

| 4   | saturation           | voltage                | VONB    | MU, MV, MW              | _        | 2.0  | 3.0  | V    | I=0.7A, VCC=                    | =15V               |

| 5   | Output To            | urn on                 | TdONT   | MU, MV, MW              | _        | 3.5  | 5.0  | μs   | VS=325V, VC                     | CC=15V             |

| 6   | delay                |                        | TdONB   | MU, MV, MW              | _        | 3.5  | 5.0  | μs   | I=0.7A                          |                    |

| 7   | time T               | urn off                | TdOFFT  | MU, MV, MW              | _        | 2.5  | 4.0  | μs   | Resistive load                  |                    |

| 8   |                      |                        | TdOFFB  | MU, MV, MW              |          | 2.5  | 4.0  | μs   |                                 |                    |

| 9   | Dead To              | op arm on              | TDT     | MU, MV, MW              | 0.3      | 1.0  | 1.8  | μs   | VS=325V, VC                     | CC=15V,            |

| 10  | time Bo              | ottom arm on           | TDB     | MU, MV, MW              | 0.3      | 1.0  | 1.8  | μs   | I=0.7A<br>Resistive load Note 1 |                    |

| 11  | Free-whee            | -                      | VFDT    | MU, MV, MW              |          | 1.6  | 2.8  | V    | I=0.7A                          |                    |

| 12  | forward vo           | ltage                  | VFDB    | MU, MV, MW              |          | 1.6  | 2.8  | V    |                                 |                    |

| 13  | Over curre reference | ent protection voltage | Vref    | RS                      | 0.45     | 0.50 | 0.55 | V    | VCC=15V                         |                    |

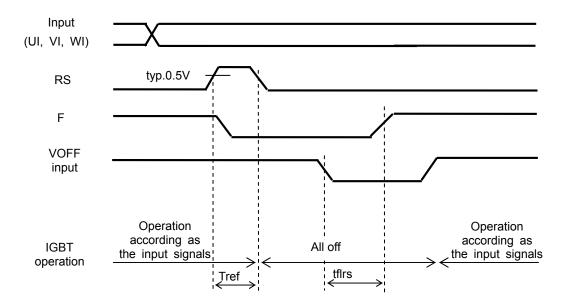

| 14  | Over curred          | ent protection         | Tref    | RS                      | _        | 5.0  | 7.0  | μs   | VCC=15V                         |                    |

| 15  | UI, VI, WI           | , Voltage              | VIH     | UI, VI, WI,             | 2.5      | _    | _    | V    | VCC=15V                         |                    |

| 16  | VOFF, CK             |                        | VIL     | VOFF, CK                | _        | _    | 1.0  | V    |                                 |                    |

| 17  | inputs               | Current                | IIL     | UI, VI, WI,<br>VOFF, CK | -10      | ı    | _    | μA   | Input =0V<br>VCC=15V            | Pull-down resistor |

| 18  |                      |                        | IIH     |                         | 1        | 1    | 100  | μA   | Input =4.5V<br>VCC=15V          | Note 2             |

| 19  | RS input             | current                | IILRS   | RS                      | -100     | _    | _    | μΑ   | RS=0V                           |                    |

|     |                      |                        |         |                         |          |      |      |      | Pull-up resiste                 | or Note 3          |

| 20  | VB supply            | Voltage                | VB      | СВ                      | 4.5      | 5.0  | 5.5  | ٧    | VCC=15V, IB                     | =0A                |

| 21  | output               | Current                | IB      | СВ                      | _        | _    | 45   | mA   | VCC=15V                         |                    |

| 22  | LVSD                 | Operating voltage      | LVSDON  | VCC,<br>MU, MV, MW      | 11.0     | 11.7 | 12.5 | V    | Note 4                          |                    |

| 23  |                      | Recovery voltage       | LVSDOFF |                         | 11.5     | 12.2 | 13.0 | V    |                                 |                    |

| 24  | F output r           | esistance              | ROP     | F                       | _        | 2.0  | 4.0  | kΩ   | I=1mA,VCC=15V Note              |                    |

| 25  |                      |                        | RON     | F                       | _        | 0.7  | 1.5  | kΩ   | I=-1mA, VCC=15V<br>Note 5       |                    |

| 26  | Fault rese           | t delay time           | tflrs   | F                       | _        | 15   | 30   | μs   | VCC=15V                         |                    |

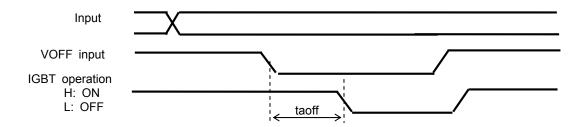

| 27  | All off dela         | ay time                | taoff   | VOFF                    | _        | 2.5  | 4.0  | μs   | VCC=15V                         |                    |

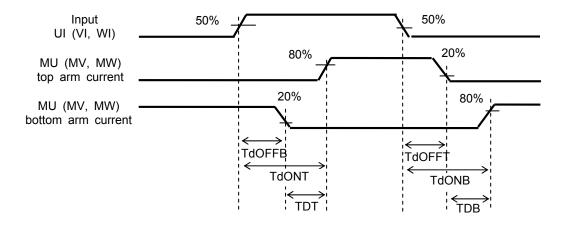

Note 1: The definition of dead time is shown in Fig. 2.4. The values of No.9 and No.10 are based on actual measurement values. Therefore, not all values of No.9 and No.10 are the same as the values calculated from the values of No.5 to No.8.

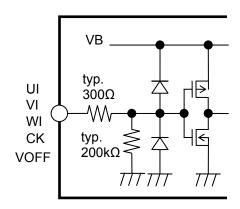

- Note 2: Internal pull-down resistances are typically  $200k\Omega$ . Fig. 2.1 is the equivalent circuit.

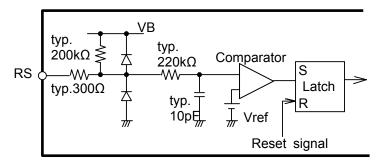

- Note 3: Internal pull-up resistance is typically 200kΩ. Fig. 2.2 is the equivalent circuit.

- Note 4: The LVSD function detects and shuts down at low VCC.

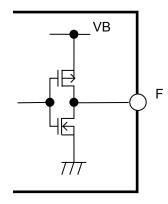

- Note 5: The equivalent circuit is shown in Fig. 2.3.

<3-input series> P. 5/16

## ECN33202SP/SPR/SPV

#### 2.3 Operating Condition

**Table 2.3 Operating Condition**

| No. | Item                  | Symbol | Pin           | Min. | Тур. | Max. | Unit | Condition   |

|-----|-----------------------|--------|---------------|------|------|------|------|-------------|

| 1   | Supply voltage        | VSop   | VS1, VS2      | 15   | -    | 450  | V    |             |

| 2   |                       | VCCop  | VCC           | 13.5 | 15   | 16.5 | V    |             |

| 3   | Clock input frequency | Fck    | CK            | 12   | 1    | 22   | kHz  |             |

| 4   | PWM input frequency   | Fpwm   | UI, VI, WI    | 12   | _    | 22   | kHz  |             |

| 5   | GH voltage            | Vgh    | GHU, GHV, GHW | -1.0 | -    | 1.0  | V    | Based on GL |

Fig. 2.1

Equivalent Circuit Around UI, VI, WI, CK, VOFF Pins

Fig. 2.2 Equivalent Circuit Around RS Pin

Fig. 2.3

Equivalent Circuit Around F Pin

<3-input series> P. 6/16

## ECN33202SP/SPR/SPV

#### 2.4 Functions and Operations

#### 2.4.1 Truth Table

Table 2.4 Truth Table

| Pin        | Input | Input Top arm              |     |  |

|------------|-------|----------------------------|-----|--|

| UI, VI, WI | L     | OFF                        | ON  |  |

|            | Н     | ON                         | OFF |  |

| VOFF       | L     | ALL OFF                    |     |  |

|            | Н     | Based on UI, VI, WI inputs |     |  |

#### 2.4.2 Dead Time

The ECN33202 generates six signals with dead time from three input signals, and the six signals control top and bottom arm IGBTs.

Fig. 2.4 Definition of Dead Time (Resistive Load)

#### 2.4.3 All Output IGBT Shutoff Function

When "L" is input to VOFF pin, all IGBTs are turned off. When "H" is input to VOFF pin, IGBTs operate based on UI, VI, WI, and RS input signals.

Fig. 2.5 Definition of taoff

<3-input series> P. 7/16

### ECN33202SP/SPR/SPV

#### 2.4.4 Over Current Protection

The ECN33202 monitors the current through the shunt resistance Rs. When the voltage at the RS pin exceeds the Vref (Vref is Typically 0.5V) of the internal detection circuit, all IGBTs are turned off and the F pin outputs "L". Input "L" at VOFF pin to reset this all off state. The F pin outputs "H" by inputting "L" after a lapse of fault reset delay time (tflrs). Lengthen the period of VOFF "L" for the fault reset delay time or more. Input "H" at VOFF pin to restart.

Just after the 15V\_VCC is input, the over current protection may operate. In this case, reset the all off state.

Fig. 2.6 Definition of Tref, tflrs

#### 2.4.5 15V\_VCC Under-Voltage Detection

When the 15V\_VCC voltage goes below the LVSD operating voltage (LVSDON), all IGBTs are turned off. When the 15V\_VCC voltage goes up, this all off state is reset at the LVSD recovery voltage (LVSDOFF).

#### 2.4.6 Input Signals at Standby Condition

Input "L" at VOFF and CK pins at standby condition.

#### 2.4.7 Clock Signal

Input the clock signal specified as follows into CK pin.

• H level = VB, L level = 0V, Duty = 50%

<3-input series> P. 8/16

### ECN33202SP/SPR/SPV

#### 3. Specifications

#### 3.1 External Parts

Table 3.1 External Parts

| Part   | Standard Value           | Usage                                  | Remarks                      |

|--------|--------------------------|----------------------------------------|------------------------------|

| C0     | 1.0μF ± 20%              | Filters the internal power supply (VB) | Stress voltage is VB (=5.5V) |

| C1, C2 | 1.0μF ± 20%              | For charge pump                        | Stress voltage is 15V_VCC    |

| D1, D2 | 600V, 1.0A<br>trr ≤100ns | For charge pump                        |                              |

| Rs     | Note 1                   | Sets over current limit                |                              |

Note 1: The over current protection setting IO is calculated as follows.

IO = Vref / Rs (A)

To determine the shunt resistance Rs for over-current protection, refer to the above IO and the Supplementary reference data in Section 4.

Fig. 3.1 Block Diagram (ECN33202 is shown inside the bold line.)

#### 3.2 Input Pins (UI, VI, WI, VOFF, CK)

In some applications, input pins may be sensitive to noise due to high impedance.

If noise is detected at an input pin, the following resistor and /or capacitor should be added.

• Resistor :  $5.6k\Omega\pm5\%$  pull-down resistor between the GL pin and input pins.

· Capacitor: 470pF±20% ceramic capacitor close to the input pins (UI, VI, WI, CK).

: 0.01µF±20% ceramic capacitor close to the input pin (VOFF).

<3-input series> P. 9/16

## ECN33202SP/SPR/SPV

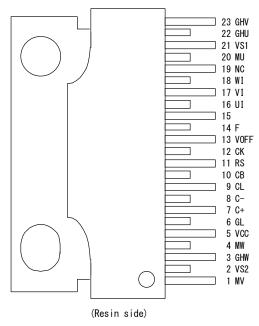

#### 4. Pin Locations

Fig. 4.1 Pin Locations

#### 5. Explanations of Pins

**Table 5.1 Explanations of Pins**

| No. | Symbol | Definition                                                             | Remarks        |

|-----|--------|------------------------------------------------------------------------|----------------|

| 1   | MV     | V phase output                                                         | Note 1         |

| 2   | VS2    | Power supply for top arm IGBTs of V and W phases                       | Note 1, Note 2 |

| 3   | GHW    | Emitter of W phase bottom arm IGBT and anode of W phase bottom arm FWD |                |

| 4   | MW     | W phase output                                                         | Note 1         |

| 5   | VCC    | 15V control power supply                                               |                |

| 6   | GL     | Control system GND                                                     |                |

| 7   | C+     | For the charge pump circuit, power supply for top arm drive circuits   | Note 1         |

| 8   | C-     | For the charge pump circuit                                            | Note 1, Note 2 |

| 9   | CL     | For the charge pump circuit                                            | Note 1         |

| 10  | СВ     | 5V power supply output                                                 |                |

| 11  | RS     | RS voltage input for over current protection                           |                |

| 12  | CK     | Clock input                                                            |                |

| 13  | VOFF   | All off input                                                          |                |

| 14  | F      | Fault signal output                                                    |                |

| 15  | _      | Feedback signal output for kit product (ECN39100 series) Open the pin. |                |

| 16  | UI     | Input control signal for U phase                                       |                |

| 17  | VI     | Input control signal for V phase                                       |                |

| 18  | WI     | Input control signal for W phase                                       |                |

| 19  | NC     | No connection                                                          | Note 3         |

| 20  | MU     | U phase output                                                         | Note 1         |

| 21  | VS1    | Power supply for top arm IGBT of U phase                               | Note 1, Note 2 |

| 22  | GHU    | Emitter of U phase bottom arm IGBT and anode of U phase bottom arm FWD |                |

| 23  | GHV    | Emitter of V phase bottom arm IGBT and anode of V phase bottom arm FWD |                |

Note 1: High voltage pin.

Note 2: The VS1, VS2 and C- pins are connected within the ECN33202 but VS1 and VS2 must also be connected by external wiring.

Note 3: Not connected to the internal chip.

<3-input series> P. 10/16

### ECN33202SP/SPR/SPV

#### 6. Inspection

Hundred percent inspection is conducted on electric characteristics at  $Ta = 25\pm5^{\circ}C$ .

#### 7. Warnings and Usage Precautions

#### 7.1 Assembling

When assembling the device on the heat sink, tightening torque range should be 0.39 to 0.78N·m.

Tab should not be soldered.

#### 7.2 Countermeasure Against Electrical Static Discharge (ESD)

- (a) The ECN33202 must be handled carefully to protect it from ESD. The material of containers or any other device used to carry semiconductor devices should be free from ESD, which can be caused by vibration during transportation. Use of electrically conductive containers is recommended as an effective countermeasure.

- (b) Everything that touches semiconductor devices, such as the work platform, machine, measuring equipment, and test equipment should be grounded.

- (c) Workers should be high-impedance grounded (around  $100k\Omega$  to  $1M\Omega$ ) while working with the semiconductor, to avoid damaging the ECN33202 by ESD.

- (d) Friction with other materials, such as high polymers, should be avoided.

- (e) When a PCB with a mounted ECN33202 is carried, ensure that electric potential is kept on the same level by the short-circuit terminals and that vibration or friction does not occur.

- (f) The humidity at assembly line to mount IC on circuit boards should be kept around 45 to 75 percents using humidifiers or such. If the humidity cannot be controlled sufficiently, using neutralization apparatus such as ionizers are effective.

#### 7.3 Note regarding Insulation between Pins

High voltages are applied between the pin numbers specified below. Hitachi advises the application of coating resin or molding treatment.

Between pin numbers: 1 - 2, 2 - 3, 3 - 4, 4 - 5, 6 - 7, 8 - 9, 9 - 10, 18 - 20, 20 - 21, 21 - 22

#### 7.4 Output Short-Circuit Protection

ECN33202 has no protection function against output short-circuit (load short-circuit, earth fault, etc.). If output is short-circuited, there is a possibility that the ECN33202 will be destroyed. Thus, be sure to protect it externally.

#### 7.5 Absolute Maximum Ratings

Regardless of changes in external conditions during use, "absolute maximum ratings" should never be exceeded in designing electronic circuits that employ the ECN33202. If absolute maximum ratings are exceeded, the ECN33202 may be damaged or destroyed. In no event shall Hitachi be liable for any failure in the ECN33202 or any secondary damage resulting from use at a value exceeding the absolute maximum ratings.

#### 7.6 Derating Design

Continuous high-loaded (high temperature, high voltage, large current) operation should be avoided and derating design should be applied, even within the ranges of the absolute maximum ratings, to ensure reliability.

<3-input series>

### ECN33202SP/SPR/SPV

#### 7.7 Safe Design

The ECN33202 may experience failures due to accident or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy or prevention of erroneous action, to avoid extensive damage in the event of a failure.

#### 7.8 Use

The ECN33202 is not manufactured to be suitable for use where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment).

Inclusion of the ECN33202 in such application shall be fully at the risk of the customer. Hitachi assumes no liability for applications assistance, customer product design, or performance.

In such cases customers are advised to ensure circuit and/or product safety by using semiconductor devices that assures high reliability or by user's fail-safe precautions or other arrangements. (If a semiconductor device fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst.)

#### 7.9 Soldering

The peak temperature of flow soldering\* must be less than  $260^{\circ}$ C, and the dip time must be less than 10 seconds. High stress by mounting, such as long time thermal stress by preheating, mechanical stress, etc, can lead to degradation or destruction. Make sure that your mounting method does not cause problem as a system.

\* Flow soldering: Only pins enter a solder bath, while the resin or tab does not.

#### 7.10 Other

See the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" for other precautions and instructions on how to deal with these kinds of products.

#### 8. Operation

- (1) Hitachi warrants performance of the ECN33202 to the specifications applicable at the time of sale in accordance with this specification. Testing and other quality control techniques are utilized to the extent Hitachi needs to meet specifications described in this document. Specific testing of all parameters of each device is not necessarily performed, except those mandated by related laws and/or regulations.

- (2) If the performance of the ECN33202 does not meet this specification within one month after the delivery, all of the appropriate lot will be tested and delivered again. However, the ECN33202 delivered more than one month ago is excluded.

- (3) Hitachi assumes no obligation for compensation for any fault in customer's goods using the ECN33202 in the marketplace. However, if Hitachi clearly has a responsibility and the ECN33202 does not meet this specification, and a customer demands for compensation within one year after the delivery of the ECN33202, the customer will be compensated by substitutions or amount of money up to worth of them.

<3-input series>

### ECN33202SP/SPR/SPV

- (4) Hitachi reserves the right to make changes in this specification and to discontinue mass production of the ECN33202 without notice. Customers are advised before purchasing to confirm that this specification of the ECN33202 is the latest version and that the ECN33202 is on mass-production status if purchasing has been suspended for one year or more.

- (5) In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this specification. Hitachi assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this specification.

- (6) No license is granted by this specification under any patents or other rights of any third party or Hitachi Power Semiconductor Device, Ltd.

- (7) This specification should not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi Power Semiconductor Device, Ltd.

- (8) For the ECN33202 (technologies) described in this specification, the followings are prohibited.

- (a) To provide to any party whose purpose in their application will hinder maintenance of international peace and safety.

- (b) To be applied to the above-described purpose by direct purchasers or any third party.

When exporting the ECN33202 (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

<3-input series> P. 13/16

## ECN33202SP/SPR/SPV

#### Supplementary Reference Data

Refer to the derating information below when designing with the ECN33202.

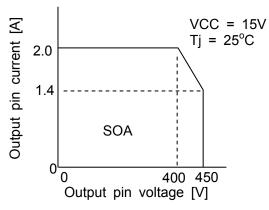

#### 1. Safe Operation Area (SOA)

It is important that the ECN33202 be used within the SOA shown in Fig. 1.1, where the current and voltage are at the MU, MV, and MW pins (motor coils).

Fig. 1.1 SOA

#### 2. General Design Derating Standards

- (a) Temperature: Junction operating temperature must be kept under 110°C.

- (b) Supply voltage: VS power supply voltage must be kept under 450V.

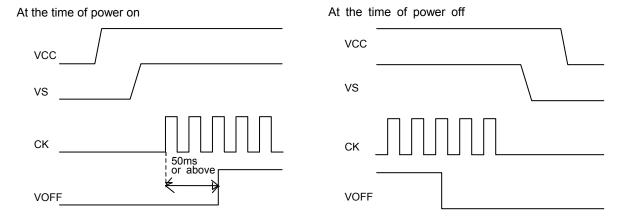

#### 3. Power Supply Sequence

Follow the power supply sequence below.

- At the time of power on ; Power on VCC → Power on VS → Input clock to CK pin → Input "H" at VOFF pin

- At the time of power off ; Input "L" at VOFF pin  $\rightarrow$  Stop inputting clock to CK pin  $\rightarrow$  Power off VS  $\rightarrow$  Power off VCC

Fig. 3.1 Power Supply Sequence at Time of Power On Fig. 3.2 Power Supply Sequence at Time of Power Off

<3-input series> P. 14/16

# ECN33202SP/SPR/SPV

#### 4. Dimensions (mm)

Fig. 4.1 Dimensions (SP, SPV) (mm)

<3-input series> P. 15/16

# ECN33202SP/SPR/SPV

Fig. 4.2 Dimensions (SPR) (mm)

### Precautions for Safe Use and Notices

If semiconductor devices are handled inappropriate manner, failures may result. For this reason, be sure to read the latest version of "Instructions for Use of Hitachi High-Voltage Monolithic ICs" before use.

This mark indicates an item about which caution is required.

#### CAUTION

This mark indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury and damage to property.

### **CAUTION**

- (1) Regardless of changes in external conditions during use "absolute maximum ratings" should never be exceed in designing electronic circuits that employ semiconductors. In the case of pulse use, furthermore, "safe operating area (SOA)" precautions should be observed.

- (2) Semiconductor devices may experience failures due to accident or unexpected surge voltages. Accordingly, adopt safe design features, such as redundancy or prevention of erroneous action, to avoid extensive damage in the event of a failure.

- (3) In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of user's fail-safe precautions or other arrangement. Or consult Hitachi's sales department staff.

(If a semiconductor devices fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst)

### **NOTICES**

- 1. This Data Sheet contains the specifications, characteristics (in figures and tables), dimensions and handling notes concerning power semiconductor products (hereinafter called "products") to aid in the selection of suitable products.

- 2. The specifications and dimensions, etc. stated in this Data Sheet are subject to change without prior notice to improve products characteristics. Before ordering, purchasers are advised to contact Hitachi's sales department for the latest version of this Data Sheet and specifications.

- 3. In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this Data Sheet. Hitachi assumes to responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this Data Sheet.

- 4. In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

- 5. No license is granted by this Data Sheet under any patents or other rights of any third party or Hitachi Power Semiconductor Device, Ltd.

- 6. This Data Sheet may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi Power Semiconductor Device, Ltd.

- 7. The products (technologies) described in this Data Sheet are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

Refer to the following website for the latest information. Consult Hitachi's sales department staff if you have any questions.

http://www.hitachi-power-semiconductor-device.co.jp/en/